100GBASE-LR4 QSFP28 1310nm 10 กม. โมดูล Hi-Optel HQSFP28-2L2

คำอธิบาย

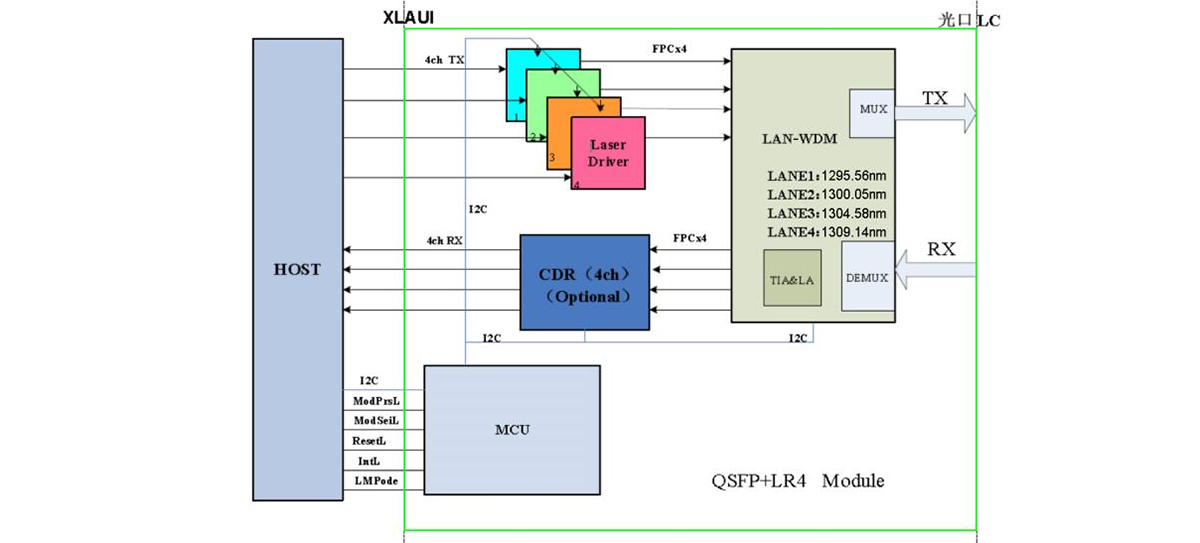

แผนภาพบล็อกของตัวรับส่งสัญญาณแสง QSFP28 LR4 แสดงอยู่ด้านล่าง

คุณสมบัติ

● รองรับอัตราบิตรวม 103.1Gb/s

● อินเทอร์เฟซทางไฟฟ้าแบบกำหนดเวลาใหม่ 4x25.78Gb/s

● เครื่องส่ง LAN-WDM บนพื้นฐาน DFB ขนาด 4x25.78Gb/s และตัวรับ PIN/TIA

● ความยาวลิงก์สูงสุด 10 กมไฟเบอร์โหมดเดี่ยว (SMF)

● รอยเท้า QSFP28 แบบเสียบปลั๊กได้ทันที

● เต้ารับ LC ดูเพล็กซ์

● แหล่งจ่ายไฟ 3.3V เดี่ยว

● การกระจายพลังงานสูงสุด<3.5W

● เป็นไปตามมาตรฐาน RoHS-6 และปราศจากสารตะกั่ว

● อินเตอร์เฟซการจัดการ I2C

● อุณหภูมิการทำงานของเคส:เชิงพาณิชย์: 0°C ถึง +70°C

แอปพลิเคชัน

● 100GBASE-LR4 100G อีเทอร์เน็ต

การปฏิบัติตาม

● QSFP28 MSA

IEEE802.3bm และ IEEE802.3ba

เอสเอฟเอฟ-8679

เป็นไปตามมาตรฐาน RoHS

อินเทอร์เฟซการตรวจสอบการวินิจฉัยแบบดิจิตอล

ฟังก์ชั่นการตรวจสอบการวินิจฉัยแบบดิจิทัลมีอยู่ใน QSFP28 LR4 การตรวจสอบแบบเรียลไทม์รวมถึงโมดูลอุณหภูมิ แรงดันไฟจ่ายโมดูล และการตรวจสอบช่องตัวส่งและตัวรับแต่ละช่อง

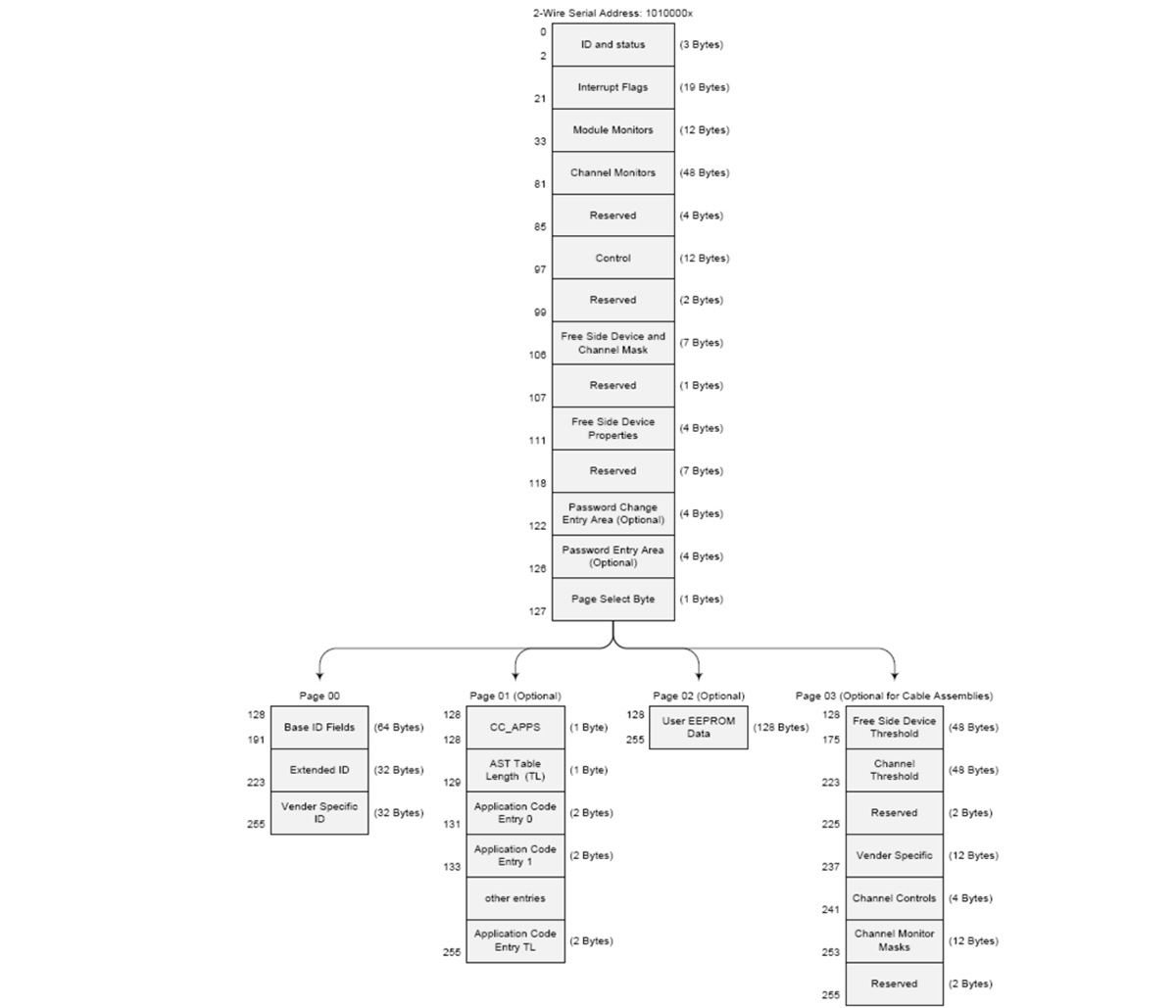

แผนที่หน่วยความจำสำหรับโมดูล QSFP28 ใช้สำหรับ ID ประจำเครื่อง การตรวจสอบแบบดิจิทัล และฟังก์ชันการควบคุมบางอย่าง

อินเทอร์เฟซจำเป็นสำหรับอุปกรณ์ QSFP28 ทั้งหมด อินเทอร์เฟซได้รับการออกแบบส่วนใหญ่หลังจาก XFP MSAตามที่กำหนดไว้ใน INF-8077i Rev.4.0 แผนที่หน่วยความจำมีการเปลี่ยนแปลงเพื่อรองรับ 4 ออปติคอลช่องและจำกัดพื้นที่หน่วยความจำที่ต้องการ ใช้วิธีการที่อยู่เดียวตามที่พบใน XFP เพจจิ้งคือใช้เพื่อให้สามารถโต้ตอบเวลาที่สำคัญระหว่างโฮสต์และโมดูล

โครงสร้างของหน่วยความจำแสดงไว้ในรูปที่ 30 พื้นที่หน่วยความจำถูกจัดเรียงเป็นหน้าเดียวด้านล่างพื้นที่ที่อยู่ 128 ไบต์และหน้าพื้นที่ที่อยู่ด้านบนหลายหน้า โครงสร้างนี้ช่วยให้เข้าถึงได้ทันเวลาที่อยู่ในเพจด้านล่าง เช่น Interrupt Flags and Monitors รายการสำคัญที่ใช้เวลาน้อยลง เช่น Serial IDการตั้งค่าข้อมูลและเกณฑ์สามารถใช้ได้กับฟังก์ชันการเลือกหน้า โครงสร้างยังให้ขยายที่อยู่โดยเพิ่มหน้าบนเพิ่มเติมตามความจำเป็น ตัวอย่างเช่น ใน table1 ด้านบนของหน้า 01 และ 02เป็นทางเลือก หน้าบน 01 อนุญาตให้ใช้งาน Application Select Table และหน้าบน 02 จัดเตรียมไว้พื้นที่อ่าน/เขียนของผู้ใช้ หน้าล่างและหน้าบน 00 จะถูกนำไปใช้เสมอ จำเป็นต้องมีหน้า 03 หากไบต์ 2บิต 2 ในหน้าล่างต่ำ ดูตารางที่ 39 สำหรับรายละเอียดเกี่ยวกับการประกาศตัวเลือกหน้าบน 01 และ 02

ที่อยู่อินเทอร์เฟซที่ใช้คือ A0xh และส่วนใหญ่จะใช้สำหรับข้อมูลที่สำคัญด้านเวลา เช่น การจัดการการขัดจังหวะ เพื่อเปิดใช้งาน "การอ่านครั้งเดียว" สำหรับข้อมูลทั้งหมดที่เกี่ยวข้องกับสถานการณ์ขัดจังหวะ หลังจากยืนยันการขัดจังหวะ IntL แล้ว โฮสต์สามารถอ่านฟิลด์แฟล็กเพื่อกำหนดช่องสัญญาณที่ได้รับผลกระทบและประเภทของแฟล็ก

ตารางที่ 1: แผนผังหน่วยความจำการวินิจฉัยแบบดิจิทัล (คำอธิบายฟิลด์ข้อมูลเฉพาะ)

| ที่อยู่ | คำอธิบาย | พิมพ์ | ทองแดงแบบพาสซีฟ, ทองแดงแบบแอคทีฟ, ออปติคัลแบบแอคทีฟ | โมดูลออปติคัล |

| 0 | ตัวระบุ (1 ไบต์) | อ่านอย่างเดียว | R | R |

| 1-2 | สถานะ (2 ไบต์) | อ่านอย่างเดียว | ดูตารางที่ 18 | |

| 3-21 | แฟล็กขัดจังหวะ (19 ไบต์) | อ่านอย่างเดียว | ดูตารางที่ 19-21 | |

| 22-33 | มอนิเตอร์โมดูล (12 ไบต์) | อ่านอย่างเดียว | ดูตารางที่ 22 | |

| 34-81 | จอภาพช่องสัญญาณ (48 ไบต์) | อ่านอย่างเดียว | ดูตารางที่ 23 | |

| 82-85 | สงวนไว้ (4 ไบต์) | อ่านอย่างเดียว | ที่สงวนไว้ | |

| 86-97 | ควบคุม (12 ไบต์) | อ่าน/เขียน | ดูตารางที่ 24 | |

| 98-99 | สงวนไว้ (2 ไบต์) | อ่าน/เขียน | ที่สงวนไว้ | |

| 100-106 | มาสก์โมดูลและแชนเนล (7 ไบต์) | อ่าน/เขียน | ดูตารางที่ 25 | |

| 107-118 | สงวนไว้ (12 ไบต์) | อ่าน/เขียน | ที่สงวนไว้ | |

| 119-122 | พื้นที่รายการเปลี่ยนรหัสผ่าน (ไม่บังคับ) (4 ไบต์) | อ่าน/เขียน | 0 | 0 |

| 123-126 | พื้นที่ป้อนรหัสผ่าน (ไม่บังคับ) 4 ไบต์ | อ่าน/เขียน | 0 | 0 |

| 127 | หน้าเลือกไบต์ | อ่าน/เขียน | R | R |